[ad_1]

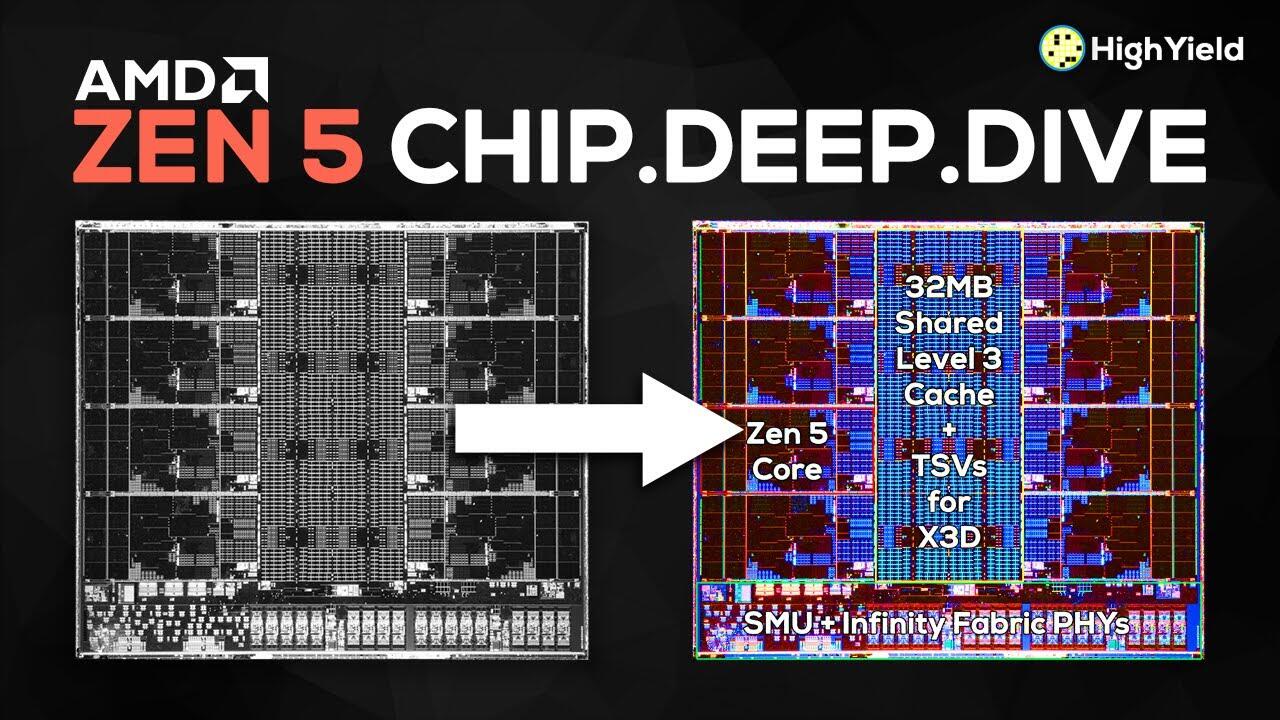

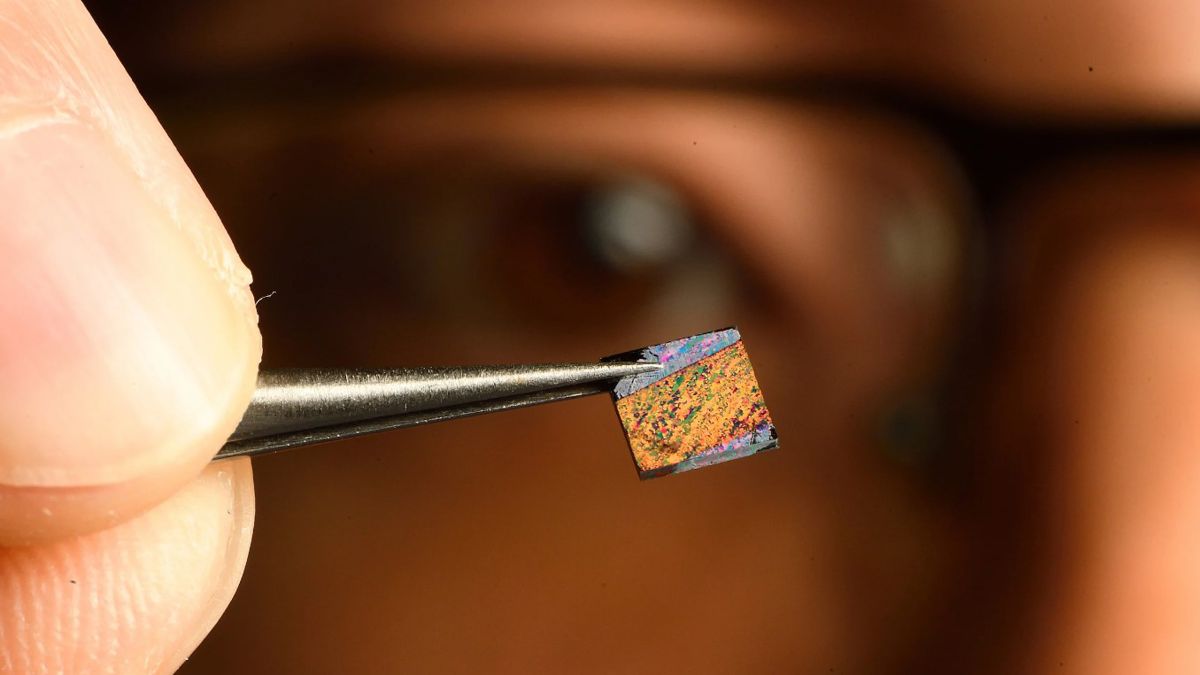

Fritzchen’s Fritzknown for extremely high-resolution so-called “die shots”, has on his Flickr account First images of an AMD Ryzen 5 9600X with a new 4 nm Zen 5 chiplet and familiar 6 nm I/O die have been released. Initial analyzes of the original images, which were over 100 GB in size, show interesting changes compared to Zen 4.

What is a die shot?

The “die” is the actual chip as it comes from the wafer, without a protective package surrounding it in the final product. On the way to high-resolution photos that show the structure of the die, removing the package is the first challenge. Fritzchen’s Fritz has been facing this challenge for years.

He made his original recordings (over 100 GB for an image composed of hundreds of individual recordings) available to the YouTube account High Yieldwho did an initial analysis of Zen 5 compared to Zen 4. With the I/O die, the result is unsurprisingly not very spectacular, but with the CPU chiplet it is a completely different story.

The I/O die: Everything is the same

The I/O die, which AMD completely re-released with Zen 4 aka Ryzen 7000 two years ago with a 2-CU iGPU, has indeed remained the same. This affects the structure as such as well as the production (TSMC N6).

The Zen 5 chiplet: Almost everything new

AMD has literally turned the CPU chiplet, which still contains eight cores and 32 MB of L3 cache, on its head. The integer part of the CPU has been completely redesigned, but the floating point unit (FPU) has also undergone fundamental changes. According to High Yield, so much has happened with the integer unit that it is currently not possible for him to accurately name the individual components. The FPU was essentially doubled to make AVX-512 possible.

The L3 cache has shrunk significantly

The real surprise is the centrally located L3 cache, because it takes up a much smaller area, even though the core production has remained the same and cache cells or their transistors hardly scale with smaller production stages.

The reason for this is not smaller cache blocks, but rather that AMD was able to pack them much more densely. As a result, the L3 cache block is now just under 16 mm² instead of the previous 24 mm² and only takes up 22.4 instead of 34.6 percent of the area of the entire chiplet.

How High Yield notes, this should have implications for X3D CPUs. In these cases, the 64 MB L3 cache (3D V-cache) was finally placed on top of the L3 cache and the L2 cache located in the cores on both sides – so cache only covered cache.

Unless AMD has also made serious changes to the 3D V-cache, this will no longer be possible on a Zen 5 chiplet – the cache would also have to cover cores, which could pose a thermal problem.

However, there are other indications that AMD has also adapted the 3D V-Cache, although the picture remains incomplete.

Much fewer TSV contacts than before?

To date, a Zen 4 chiplet has had over 24,000 so-called TSV contact areas in the L3 and L2 cache. TSV stands for Through-Silicon Via and is called silicon via in German. The vertical connection technology is used to connect stacked dies and has advantages over so-called wire bonding with fine wires only at the edges of the chips stacked on top of each other.

In Zen 3 and Zen 4, the data-transmitting TSVs were found in two rows within the L3 cache, and the power-transmitting TSVs in Zen 4 were in the L3 cache and in the L2 cache.

In the photos of the Zen 5 chiplet, however, only around 9,000 such, much smaller contacts have been found so far, exclusively in two rows in the L3 cache.

Either way High Yieldsomething else was overlooked here, or AMD could have really decided to put a double-stacked and therefore smaller cache chip on top of the chiplet’s L3 cache.

The analysis is still in its early stages

Not only the new integer unit, but also the current state of knowledge regarding the number of TSV contact surfaces still raise questions.

[ad_2]

Source link